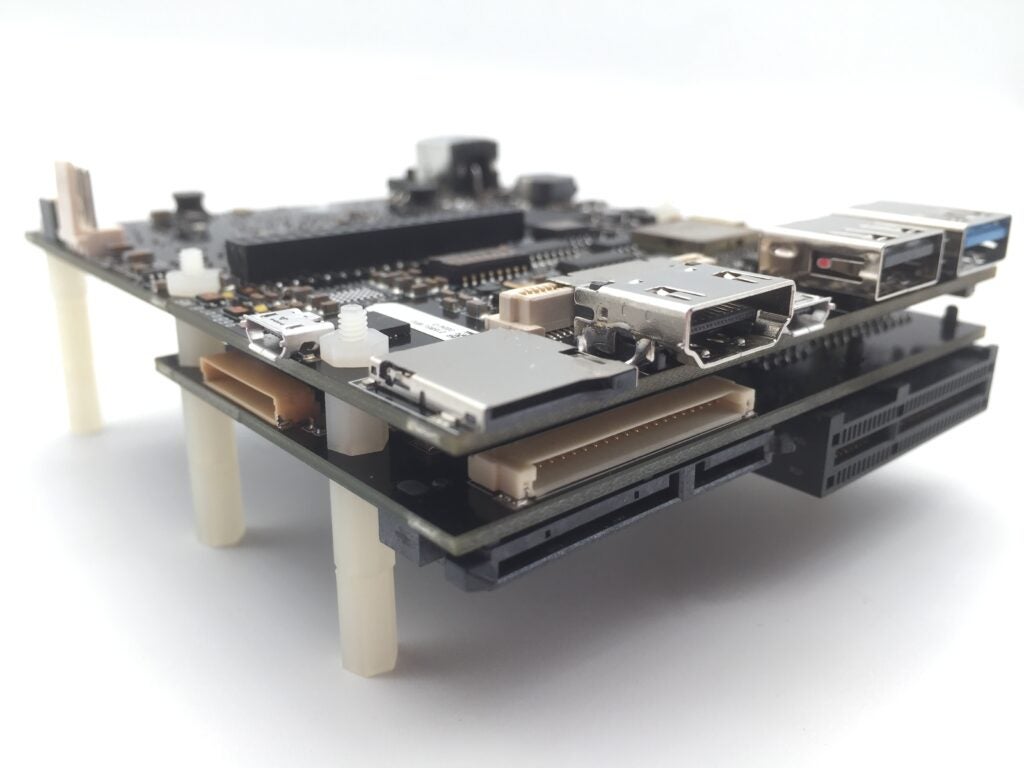

Today, the Civil Infrastructure Platform (CIP) Project is debuting the Renesas RZ/G2M-96CE board, based on the Arm 64-bit architecture, at Embedded Linux Conference. It is the first-ever using Arm 64-bit architecture that the CIP project will support.

The CIP project aims to support the reference hardware in the project’s Super Long Term Support (SLTS) Linux Kernels and minimal reference filesystem, CIP Core. Testing of the reference hardware will be done using CIP’s customised kernelci and LAVA instances and B@D. This makes it easy for software developers to make the most of the software developed by CIP and allows them to quickly and easily develop industrial applications.

The RZ/G2M-96CE board is based on the Linaro 96boards extended consumer specification. This design allows for rapid prototyping for application, kernel and hardware engineers. The RZ/G2M-96CE board development kits will be available Q1 2019.

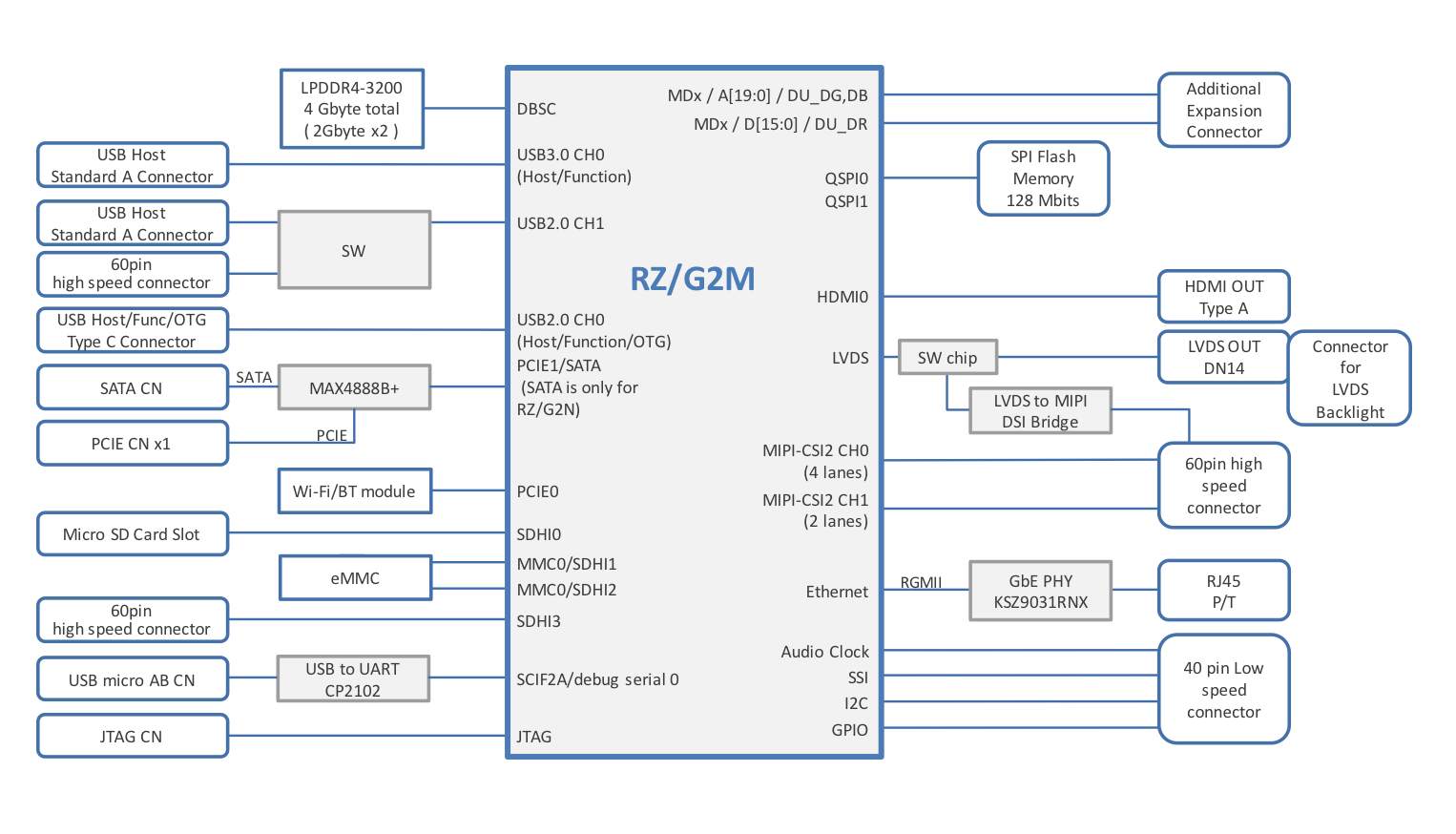

RZ/G2M-96CE board Block Diagram (Preliminary*) includes:

The RZ/G2M-96CE joins the current list of CIP-supported embedded hardware including:

- RZ/G1M iWave Qseven Development Kit (Armv7)

- AM335x Beaglebone Black (Armv7)

- QEMU x86_64

CIP will be showing a selection of the reference hardware, including the RZ/G2M-96CE board, at their booth at the Embedded Linux Conference Europe 2018. Stop by to learn more about the project. For additional information about how Renesas is providing the solutions using CIP kernel on the RZ/G2M-96CE board, please visit here for details.